组成原理速成

概论、运算

字、字长、机器字长、指令字长、存储字长、数据字长的区别和联系是什么?

字和字长的概念不同。字用来表示被处理信息的单位,用来度量数据类型的宽度,如x86机器中将一个字定义为16位。

机器字长、指令字长和存储字长,三者在数值上可以相等也可以不等,视不同机器而定。所谓字长,一般指机器字长,即计算机的位数,通常指CPU内部用于整数运算的数据通路的宽度,也就是计算机一次能处理的二进制数的长度。 因此字长等于CPU内部用于整数运算的运算器位数和通用寄存器宽度,它反映了计算机处理信息的能力。指令字长:一个指令字中包含的二进制代码的位数。 存储字长是一个存储单元中的二进制代码的位数,等于 MDR 的位数,一般取存储字长的整数倍,若指令字长等于存储字长的2倍,则需要2个访存周期来取出一条指令;若指令字长等于存储字长,则取指周期等于机器周期。早期的存储字长一般与指令字长、字长相等,因此访问一次主存便可取出一条指令或一个数据。随着计算机的发展,指令字长、字长都可变,但必须都是字节的整数倍。数据字长是数据总线一次能并行传送信息的位数。

并行加法器

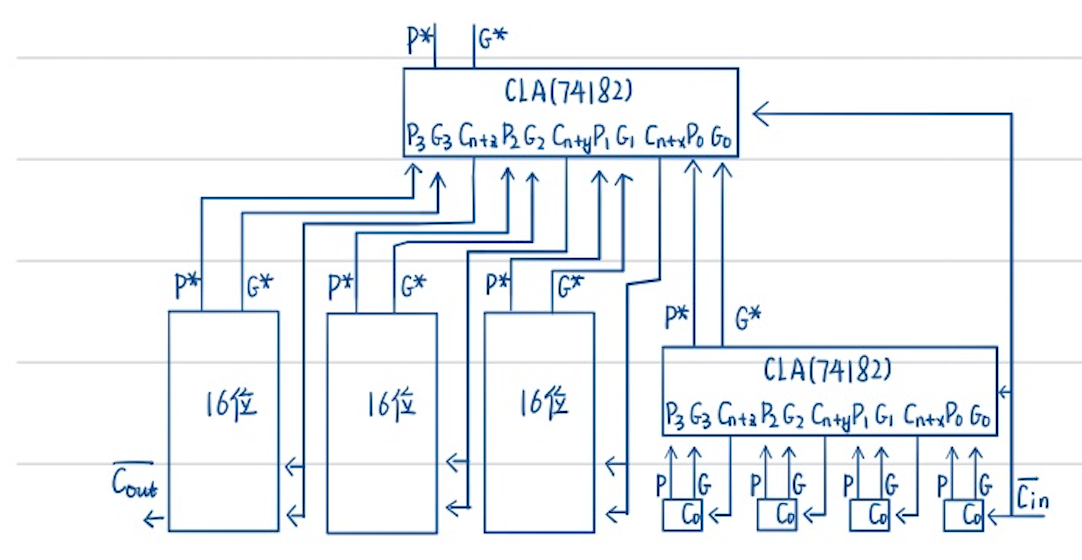

原理:$C_i$仅与$A_i$、$B_i$及最低进位$C_0$有关. 设计:同时为了降低位数过多时电路的复杂性,进行分组。可通过将CLA(先行进位)部件或全先行进位加法器串接起来实现。例如,对于16位加法器,可以分成4组,组内为4位先行进位,组间串行进位。 为了进一步提高运算速度,也可以采用组内和组间都并行的进位方式。因为两级先行进位加法器组内和组间都采用先行进位方式,其延迟和加法器的位数没有关系。所以,实际电路中通常采用两级或多级先行进位加法器。

而对于带符号数的运算,标记信息如下(把减法看作加法):

仅当两个符号相同的数相加或两个符号相异的数相减才可能产生溢出。若符号位的进位 $C_s$ 与最高数位的进位 $C_1$ 相同,则说明没有溢出,否则表示发生溢出。

浮点数

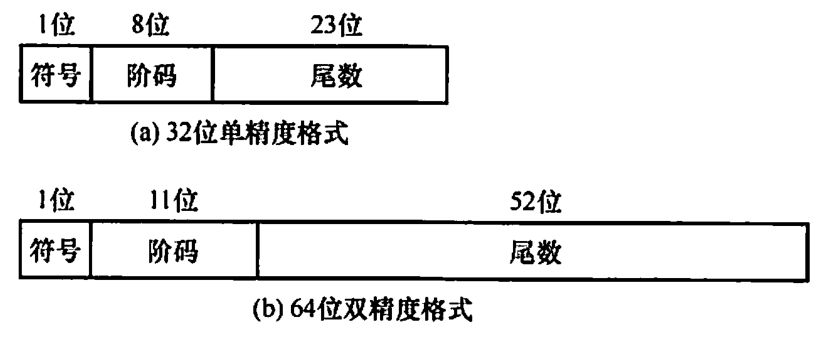

说白了就是,尾数左移(小数点右移)阶码位。float的阶码偏置为127,double为1023。规格化规定非零的浮点数在尾数的最高数位上保证是一个有效值,即调整阶码:原码表示时,正数的规格化形式为 0.1xx;负数的规格化形式为1.1x … x。类似地,补码的规格化表示是小数点后一位与符号位不同。 对于浮点数的计算,引入概念移码:即对补码的符号位取反。

如果运算结果尾数出现双符号位(正溢出01/负溢出10)情形,需要右规:阶码加1,尾数右移。

存储器概念速成

常识

MROM:只能读不能写;PROM:写一次后就不可更改。

EPROM 不仅可以由用户利用编程器写入信息,而且可以对其内容进行多次改写。但是 EPROM 的编程次数有限,且写入时间过长,不能取代 RAM。

CD-ROM 即只读型光盘存储器,采用串行存取方式,其访问方式是顺序访问,不属于只读存储器ROM 。

闪存是 E2PROM 的进一步发展,可读可写,但依然是 ROM 的一种,写入时必须先擦除原有数据,因此写速度比读速度要慢不少。

DRAM 采用传两次地址的策略,所以地址线为正常的一半。芯片引脚个数取决于行地址线和列地址线中的较大值,每次刷新开销取决于行数。Cache常用SRAM组成。

cache位计算

主存地址可分为 标记Tag、组号(容量 / 主存块大小 / 路数)、块内地址三部分,三者之和为 主存地址位数。计算单位:B

主存物理地址也可以是由TLU实页号和页内地址拼接。

所有的cache行都会对应一个标记项,用于标记当前cache行保存的数据状态。cache行的位数=cache行标记项位数+cache块位数,其中cache行标记项结构如下: 有效位1bit(是否有数据) | 标记位(主存行号,计算同Tag) | 脏位(写回法中存在1bit) | 替换控制位

式中, h是命中率。

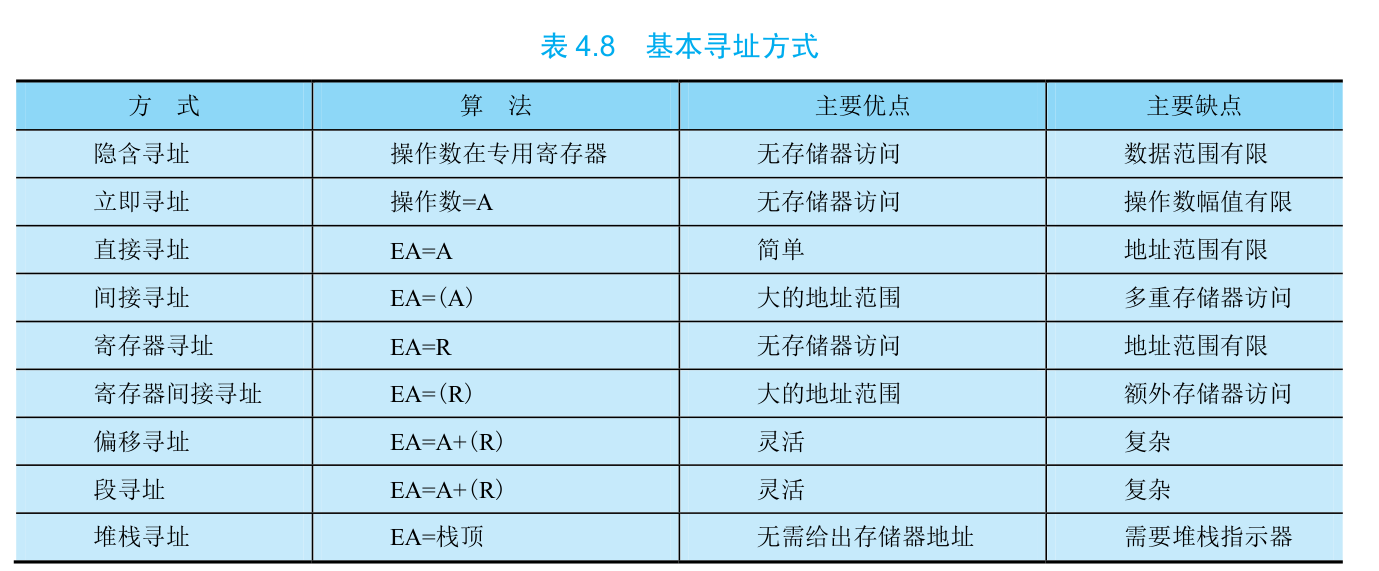

寻址方式

参考: 计算机组成原理习题参考答案 - 飞书文档 (feishu.cn)

《2023计算机组成原理考研复习指导 (王道论坛) 》

最后更新于